At SK hynix, we know how rapidly technology shifts and evolves, and how important it is for our engineers, developers, researchers and strategists to respond quickly, carefully and efficiently to meet the needs of our customers.

In November 2018, we succeeded again in providing another industry first and opened up a new sector in the DRAM space. We developed 16Gb (Gigabits) DDR5 (Double Data Rate 5) DRAM and achieved the industry’s first to meet the Joint Electron Device Engineering Council (JEDEC) standards.

In this piece, we’ll look at how DDR5 will lead the industry as one of the world’s most powerful memory in the near future and how it surpasses its predecessors.

Increased computing performance requires higher memory bandwidth

DDR5 can offer more than two times the bandwidth compared to DDR4. This is incredibly important in order to process the intensive data generated by technologies including big data, artificial intelligence (AI), and machine learning, which are leading the 4th Industrial Revolution. Overall, businesses are utilizing the real-time data in diverse ways. As such demand increases, the server system that processes the huge data is advancing quickly to meet the needs.

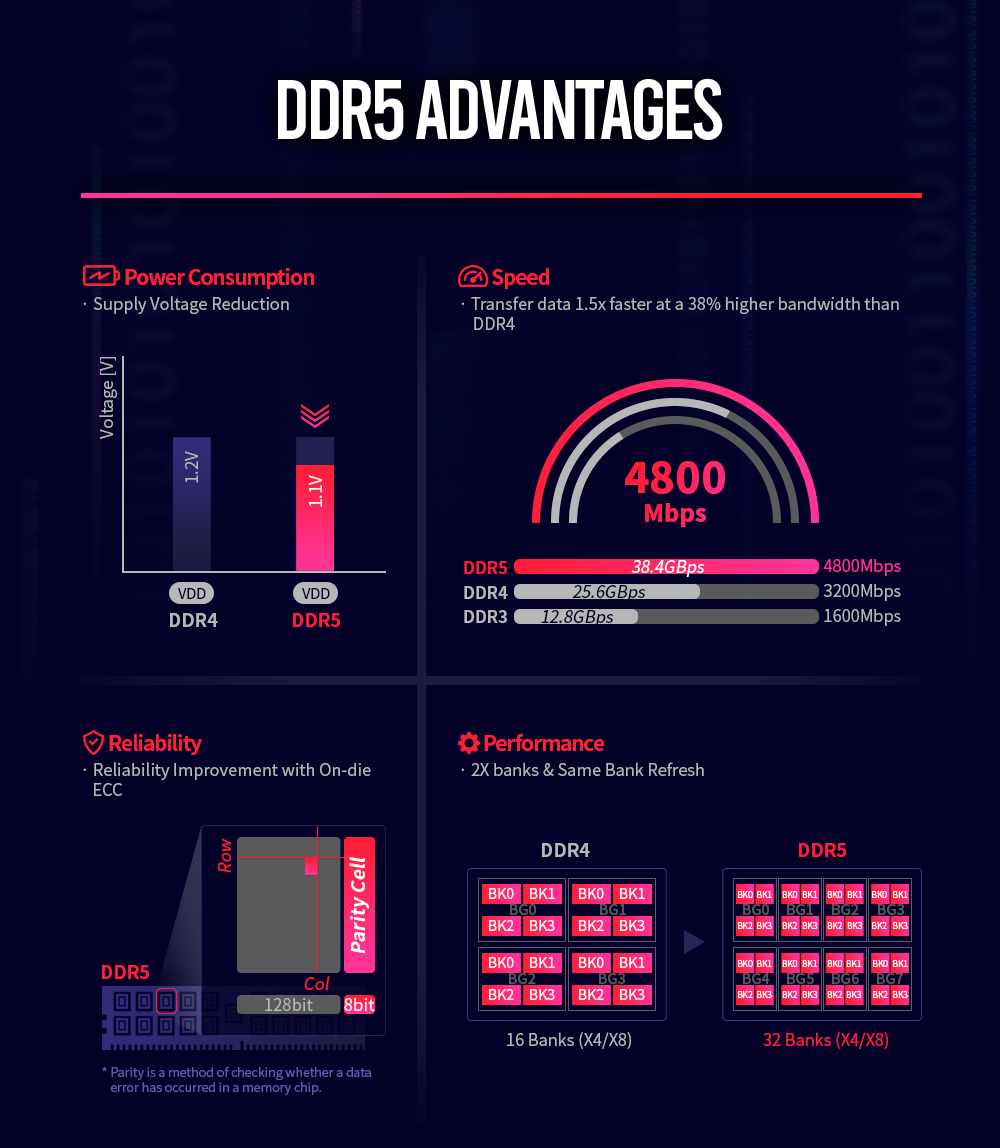

The number of CPU cores has dramatically increased to deliver higher throughput, from only 4 cores to even 64 cores for servers, and it is expected to increase continuously. As the number of cores increases, the demands on memory bandwidth are also increasing. To this end, we are preparing DDR5 that supports more than twice the DDR4’s 3200Mbps.

When we switched from DDR3 to DDR4 in 2013 the increase in bandwidth per dual in-line memory module (DIMM) was increased by 33% from 1600Mbps to 2133Mbps. However, when developing DDR5, the goal was to achieve more than 4800Mbps, which would be a more than 50% increase of the bandwidth per DIMM.

Scalability

In order to increase the memory bandwidth more than twice compared to DDR4, the amount of data processed within the same unit of time must be doubled. DDR5 will provide increased performance, capacity, and power and cost efficiency previously not available to DDR4, and various features are adopted in DDR5 as below to support the increase of memory bandwidth.

Firstly, DDR5 adopted 32banks1 structure based on 8 bank groups, which is twice as many as DDR4’s 16banks structure using 4 bank groups. This helped double DDR5’s memory access availability compared to DDR4.

Secondly, DDR5’s burst length (BL)2 is increased to 16 compared to 8 of DDR4, which is another key feature to double memory access availability.

Thirdly, DDR4 cannot perform other operations while refreshing, so it cannot be accessed from the system during refresh timing. However, DDR5 adopted Same Bank Refresh function, allowing the system to access other banks when certain banks are operating, thus improving memory access availability.

Lastly, there are many difficulties in terms of signal integrity with the large number of channels and DIMMs/Sockets in the server system. However, by adopting a Decision Feedback Equalization (DFE) circuit, which eliminates reflective noise during the channels’ high-speed operation, DDR5 increased the speed per pin considerably.

Reliability and efficiency

DDR5 provides a power-efficient design and improved reliability features, while delivering increased performance compared to DDR4.

First of all, with an operating voltage of 1.1V, lowered from DDR4’s 1.2V, DDR5 aims to reduce power consumption per bandwidth by more than 20% of its predecessor.

On-die error correction code (ECC)3 and error check and scrub (ECS), which were first to be adopted in DDR5, also allow for more reliable technology node scaling by correcting single bit errors internally. Therefore, it is expected to contribute to further cost reduction in the future. ECS records the DRAM defects and provides the error counts to the host, thereby increasing transparency and enhancing the reliability, availability, and serviceability (RAS) function of the server system.

Growing demand and agile technology

According to the market research company International Data Corporation (IDC), demand for DDR5 was expected to rise from 2020 and account for 22% of the total DRAM market in 2021 and 43% in 2022.4 SK hynix is planning to lead the market by actively responding to customer demands for ultra-high-speed, high-capacity memory, starting with 10nm-class 16Gb DDR5.

“In the 4th Industrial Revolution, which is represented by 5G, autonomous vehicle, AI, augmented reality (AR), virtual reality (VR), big data, and other applications, DDR5 DRAM can be utilized for next-gen high performance computing (HPC) and AI-based data analysis,” said Sungsoo Ryu, Head of DRAM Product Planning at SK hynix. “DDR5 will also offer a wider range of density based on 16Gb and even 24Gb monolithic die, in order to meet the needs of cloud service customers. By supporting higher density and performance scalability compared to its predecessor, DDR5 has set a firm foothold to lead the era of big data and AI. With this, SK hynix will secure a competitive edge in the premium server market while providing distinguished memory solutions to customers.”

SK hynix will start the mass-production of its DDR5 memory chip this year. At the same time, we will pursue the research and development of DRAM technologies to lead the next generation of semiconductors. We are positioning ourselves to keep on delivering our innovative, high-performance and reliable products to more people in even bigger, bolder ways.

1Bank: A data-storing unit which can be activated or deactivated independently. Data within an activated bank is capable of process read and write operation sequentially.

2Burst Length (BL): The amount of data which is input/output based on a single read/write command in DRAM.

3Error correction code (ECC): Error correction code detects and corrects internal data errors.

4″Worldwide DRAM Demand and Supply 4Q19–4Q20 and 2020–2024 Update”, Mar 2020, International Data Corporation.