SK hynix recently achieved another groundbreaking milestone by overcoming the limits of highly miniaturized DRAM process technology. In August 2024, the company announced that it had successfully developed the world’s first 16 gigabit (Gb) DDR5 DRAM using the 1c1 node, the sixth generation of the 10 nm process. Following the development of advanced HBM2 for AI applications, the company’s breakthrough in 1c process technology further solidifies its DRAM leadership.

11c: The sixth generation of the 10 nm DRAM process technology, which was developed in the order of 1x-1y-1z-1a-1b-1c.

2High Bandwidth Memory (HBM): A high-value, high-performance product that possesses much higher data processing speeds compared to existing DRAMs by vertically connecting multiple DRAMs with through-silicon via (TSV).

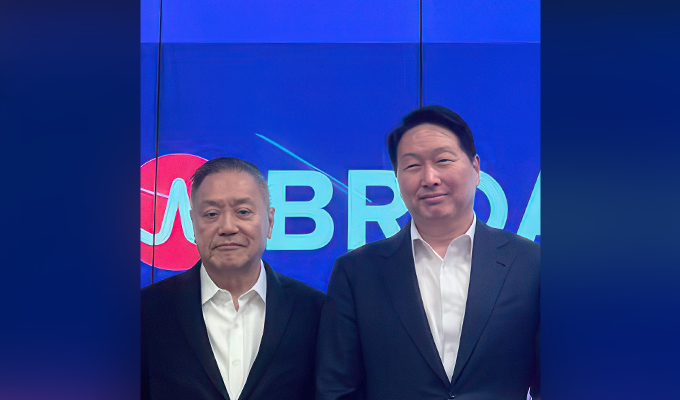

To find out more about SK hynix’s technological capabilities and DRAM roadmap as well as the development of 1c technology, the newsroom held a roundtable with key project members of the 1c DDR5. Six vice presidents from the company took part in the discussion: Taekyoung Oh of the 1c Technology Taskforce (1c Tech TF); Joohwan Cho of DRAM Design; Youngmann Cho of DRAM Process Integration (DRAM PI); Changkyo Jung of DRAM Product Engineering (DRAM PE); Sooyong Son of Development Test; and Hyungsoo Kim of DRAM Application Engineering (DRAM AE), who led the development of the 1c technology.

From left: Hyungsoo Kim (DRAM AE), Youngmann Cho (DRAM PI), Taekyoung Oh (1c Tech TF), Joohwan Cho (DRAM Design), Changkyo Jung (DRAM PE), and Sooyong Son (Development Test)

Journey to 1c: A Technological Breakthrough Achieved Through Collective Efforts

The 1c technology is an ultra-fine memory fabrication process in the low 10 nm range. Built using the 1c node, the 16 Gb DDR5 reaches an operating speed of 8 gigabits (Gbps) per second, an 11% increase over the previous generation—1b DDR5—and offers more than a 9% improvement in power efficiency. In addition to achieving performance gains, SK hynix developed new materials for the EUV lithography3 process and maximized efficiency through design innovations, resulting in both process optimization and cost reductions.

3Extreme ultraviolet (EUV) lithography: A semiconductor manufacturing technique that uses extreme ultraviolet light to create intricate patterns on silicon wafers.

To achieve these advancements and ultimately develop 1c technology, SK hynix had to overcome numerous technical challenges. This roundtable highlights the contributions of each department to achieve this feat, lifting the lid on how the engineering team secured the coveted “world’s first” title.

From left: Hyungsoo Kim, Taekyoung Oh, and Youngmann Cho discuss the company’s approach to developing 1c technology

Taekyoung Oh (1c Tech TF): “The primary goal of the 1c Tech TF, which led to the development of 1c technology, was to be the ‘first to develop.’ To achieve this, we chose a strategy that expanded upon the already proven 1b platform. We also streamlined the traditional three-stage development process—testing, design, and mass-production readiness—into a two-stage process, focusing only on design and mass-production readiness. For complex technical elements, such as the capacitor module, we integrated their development directly into the mass production process. As a result, we reduced the development time of 1c technology by two months compared to the previous generation.”

Joohwan Cho (DRAM Design): “Leveraging our experience with the proven 1b technology reduced technical risks, but the smaller cell size and increased resistance still posed significant challenges. To tackle these issues, we introduced several design innovations, including higher circuit density and enhanced sensing performance, which boosted data processing speeds and reduced power consumption. Additionally, through close collaboration with the manufacturing side, we maximized the number of net dies4 to improve cost competitiveness.”

Youngmann Cho (DRAM PI): “Our approach of expanding the 1b platform proved to be effective in reducing trial and error during the process refinement of 1c technology. Leveraging our experience with 1b, we were able to predict and resolve potential issues in 1c technology in advance. In particular, by identifying and addressing quality risks early on such as transistor degradation5 as well as applying new materials, we were able to secure the reliability of the miniaturized devices.”

4Net die: The number of viable chips (die) that can be produced from a single wafer during the semiconductor manufacturing process.

5Degradation: The deterioration of an insulator’s chemical and physical properties caused by external or internal factors.

From left: Changkyo Jung, Sooyong Son, and Joohwan Cho talk about overcoming challenges during the development process

Changkyo Jung (DRAM PE): “When developing new technology, it’s inevitable to encounter new problems that previously didn’t exist. As processes become more miniaturized, different characteristics become increasingly critical, leading to potential issues such as yield loss. For 1c technology, we utilized trimming6 techniques to enhance key performance levels, securing both yield and quality.”

6Trimming: A technique that boosts performance by utilizing electronic fuses (eFuse) without requiring changes to the semiconductor design.

Sooyong Son (Development Test): “For our department, a major challenge was reducing the test duration for 1c DDR5 products to meet the development timeline. In particular, we conducted development almost simultaneously with other key products, so we needed to improve the testing efficiency. To address this, we expanded our testing infrastructure and strategically deployed implementation systems, allowing us to complete the testing process ahead of schedule.”

Hyungsoo Kim (DRAM AE): “From our point of view, the biggest technical challenge was validating the ultra-high-speed and high-performance characteristics of the 1c DDR5. To ensure the system-level functionality of the product, which achieved the industry’s highest speed, we developed our own verification infrastructure capable of operating at 8 Gbps for the first time. Additionally, we independently developed software that could both verify and predict potential defects, securing the company a unique competitive edge.”

The Power of ‘One Team’: Establishing Unparalleled Technological Leadership

What is the driving force behind SK hynix’s ability to demonstrate unparalleled technological leadership in the DRAM market? All the participants in the roundtable unanimously emphasized “systematic collaboration” and SK hynix’s “one team” spirit.

Taekyoung Oh singles out collaboration as the key to successfully developing 1c technology

Taekyoung Oh (1c Tech TF): “I believe SK hynix’s technology development capabilities are improving through innovations across multiple areas. These innovations include enhancements in work methods such as taskforce operations, platform-based development, and early mass production fab operation strategies. Above all, I think it is the ‘one team’ spirit of the members that has driven all the achievements. The implementation of the two-stage development process, the development of new materials to improve EUV patterning performance, and cost reduction would not have been possible without a solid foundation of collaboration.”

Changkyo Jung says the company’s “one team” spirit helped to quickly identify and resolve issues

Changkyo Jung (DRAM PE): “The most important factor in the development process of 1c technology was the ‘one team’ culture. To overcome the many technical challenges that come with being the ‘first’, close collaboration between teams allowed us to identify and resolve issues early on in the process. In particular, seamless collaboration with the design and process departments was crucial for the DRAM PE department in optimizing the screening process.”

Hyungsoo Kim claims close customer communication is vital for DRAM development

Hyungsoo Kim (DRAM AE): “As microfabrication processes become more complex, a multitude of technical challenges emerge. However, I believe the company’s strength to overcome these difficulties ultimately comes from our ‘one team’ spirit, with multiple related teams working toward the same goal.

“Along with a strong internal collaboration, cooperation with customers is also crucial. DRAM is a product that operates within the customer’s system, so their perspective must be considered throughout the entire development process—from product planning to the design, process, testing, and validation stages. It is essential to conduct continuous communication and technical cooperation with customers to achieve our goals.”

Beyond 1c: Maintaining Leadership in Next-Gen DRAM Technology

The greatest significance of 1c technology’s development is that it will be applied across all of SK hynix’s next-generation DRAM product lines, including HBM, LPDDR7, and GDDR8. What innovations will 1c technology drive, and how will SK hynix’s DRAM evolve moving forward?

7Low Power Double Data Rate 5 Turbo (LPDDR5T): Low-power DRAM for mobile devices, including smartphones and tablets, aimed at minimizing power consumption and featuring low voltage operation. LPDDR5T is an upgraded product of the 7th generation LPDDR5X and will be succeeded by the 8th generation LPDDR6.

8Graphics DDR (GDDR): A standard specification of graphics DRAM defined by the Joint Electron Device Engineering Council (JEDEC) and specialized for processing graphics more quickly. It is now one of the most popular memory chips for AI and big data applications.

Sooyong Son says that 1c DDR5 is only the beginning of the company’s 1C DRAM lineup

Sooyong Son (Development Test): “The successful development of 1c has demonstrated SK hynix’s superior technological edge, but 1c DDR5 is only the beginning. Going forward, we expect that 1c technology will be integrated into a wide range of DRAM products, driving sustainable growth and innovation while fully meeting the diverse needs of our customers.”

Youngmann Cho states that innovation will help SK hynix overcome DRAM scaling challenges

Youngmann Cho (DRAM PI): “Miniaturization is set to continue as DRAM technology advances beyond 1c. Especially when transitioning to sub-10 nm nodes, there are expected to be limitations in current methods. Overcoming these challenges will require not only maximizing material and equipment performance, but also innovations such as shifting from 2D to 3D cell structures and adopting heterogeneous integration. To address this, SK hynix is continuously enhancing its DRAM development system.”

Joohwan Cho claims preparation is crucial for maintaining DRAM leadership

Joohwan Cho (DRAM Design): “For the company to maintain DRAM technology leadership, we must proactively prepare core technologies in advance based on a long-term technology roadmap. On the design side, we are advancing our systems to accurately predict risks associated with next-generation microfabrication processes, reducing the burden on our teams and strengthening the company’s competitiveness.”

SK hynix plans to finish preparations for the mass production of the 1c DDR5 product within 2024 and begin full-scale market supply from 2025. The 1c technology, which delivers both exceptional performance and cost competitiveness, is expected to further strengthen the company’s leadership. To conclude, the roundtable participants shared their reflections and aspirations as pioneers of the new DRAM paradigm.

The project members plan to build on their success by developing next-gen products in the future

Taekyoung Oh (1c Tech TF): “Being the first to develop 1c technology is not the finish line. We plan to continue to address any gaps and enhance mass production yield and cost competitiveness, thereby ensuring that SK hynix maintains its leadership position.”

Joohwan Cho (DRAM Design): “SK hynix has solidified its position as a true leader in DDR5 development. Building on the success of 1c technology, we will continue to enhance our competitiveness to deliver innovative products in 1d and future generations.”

Youngmann Cho (DRAM PI): “As demand for AI memory surges, customer expectations for high-performance memory are rising as well. The successful development of 1c DDR5 is a highly encouraging milestone. Building on this success, we will continue working to position SK hynix’s DDR5 at the forefront of the high-performance AI memory market.”

Changkyo Jung (DRAM PE): “I’m happy and proud that SK hynix has proven its world-class technology leadership through its timely delivery of products needed by the market, strengthening customer trust. Moving forward, we will continue to solve yield and quality challenges to launch even more refined products.”

Sooyong Son (Development Test): “This achievement is the result of long-term efforts. Building on the SKMS9, we will continue working with our team to drive growth and development through an excellent corporate culture and ‘one team’ collaboration.”

9SK Management System (SKMS): SK Group’s business management system comprised of SK’s management philosophy and the methodology to implement this approach into actual management.

Hyungsoo Kim (DRAM AE): “SK hynix’s 1c DDR5 will set the standard for high-performance server systems and will lead the market with its outstanding technological prowess. This achievement reflects the efforts and dedication of all the team members involved in the project. We will continue to work together to uphold our ‘world’s best’ title.”