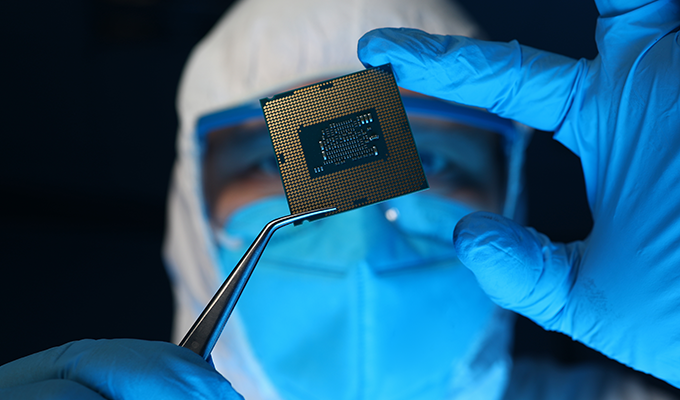

The packaging process, where different parts of a component are connected together, can be an overlooked aspect of semiconductor manufacturing. In the past, some in the industry considered packaging to be a rudimentary part of the process considered on the back-end.

Packaging, though, is now getting a fresh look as the semiconductor industry seeks to pack even more performance and capabilities into less space. In this EE Times column, SK hynix Project Leader Ho-Young Son provides new insights into how packaging can push the boundaries of memory chips and system performance overall.

He explains how advanced technologies, such as TSV (through-silicon via) and Fan-out wafer-level packaging, are helping create even smaller, thinner memory chips with higher capacities. These packaging techniques also have added benefits, such as more efficiently dissipating heat.

To find out more, please visit EE Times to read the full column titled “Advanced Packaging Technologies Overcoming the Memory System Performance and Capacity Limitation”.

ByHo-Young Son, Ph.D.

PL (Project Leader) of IIP (Intergrated Interconnect & Packaging) Team